# SN8P2240 Series

**USER'S MANUAL**

SN8P2242 SN8P22421 SN8P2241

**SONIX 8-Bit Micro-Controller**

SONIX reserves the right to make change without further notice to any products herein to improve reliability, function or design. SONIX does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. SONIX products are not designed, intended, or authorized for us as components in systems intended, for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SONIX product could create a situation where personal injury or death may occur. Should Buyer purchase or use SONIX products for any such unintended or unauthorized application. Buyer shall indemnify and hold SONIX and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that SONIX was negligent regarding the design or manufacture of the part.

#### **AMENDMENT HISTORY**

| Version | Date       | Description                                                                       |

|---------|------------|-----------------------------------------------------------------------------------|

| VER 0.1 | 2009/12/03 | First version is released.                                                        |

| VER 0.2 | 2010/03/11 | 1. Add Note for USB_INT_EN register in <u>9.5.4 USB ENABLE CONTROL REGISTER</u> . |

|         |            | 2. Add EP0_IN_STALL at IHRCU.                                                     |

|         |            | 3. Add EP0_OUT_STALL at IHRCL.                                                    |

| VER 0.3 | 2010/03/24 | Modify CH12 , Regulator GND current 80uA => 60mA                                  |

| VER 0.4 | 2010/03/30 | Modify CH12 , I/O source current and sink current.                                |

|         |            | 2. Modify CH12, Supply current.                                                   |

|         |            | 3. Modify CH13, Add P0.0 to programming pin                                       |

| VER 1.0 | 2010/04/07 | Modify CH12 , Supply current with USB Function Enable.                            |

| VER 1.1 | 2010/07/12 | 1. Add SN8P2241P( DIP 14 pins)                                                    |

# **Table of Content**

|   | AMENDMENT HISTORY                         | 2  |

|---|-------------------------------------------|----|

| 1 | PRODUCT OVERVIEW                          | 7  |

|   | 1.1 FEATURES                              | 7  |

|   | 1.2 SYSTEM BLOCK DIAGRAM                  |    |

|   | 1.3 PIN ASSIGNMENT                        | 9  |

|   | 1.4 PIN DESCRIPTIONS                      | 10 |

|   | 1.5 PIN CIRCUIT DIAGRAMS                  | 11 |

| 2 | CENTRAL PROCESSOR UNIT (CPU)              | 12 |

|   | 2.1 MEMORY MAP                            |    |

|   | 2.1.1 PROGRAM MEMORY (ROM)                |    |

|   | 2.1.1.1 RESET VECTOR (0000H)              | 13 |

|   | 2.1.1.2 INTERRUPT VECTOR (0008H)          | 14 |

|   | 2.1.1.3 LOOK-UP TABLE DESCRIPTION         | 16 |

|   | 2.1.1.4 JUMP TABLE DESCRIPTION            |    |

|   | 2.1.1.5 CHECKSUM CALCULATION              | 20 |

|   | 2.1.2 CODE OPTION TABLE                   | 21 |

|   | 2.1.3 DATA MEMORY (RAM)                   |    |

|   | 2.1.4 SYSTEM REGISTER                     |    |

|   | 2.1.4.1 SYSTEM REGISTER TABLE             | 23 |

|   | 2.1.4.2 SYSTEM REGISTER DESCRIPTION       | 23 |

|   | 2.1.4.3 BIT DEFINITION of SYSTEM REGISTER |    |

|   | 2.1.4.4 ACCUMULATOR                       | 26 |

|   | 2.1.4.5 PROGRAM FLAG                      | 27 |

|   | 2.1.4.6 PROGRAM COUNTER                   | 28 |

|   | 2.1.4.7 Y, Z REGISTERS                    | 31 |

|   | 2.1.4.8 R REGISTERS                       |    |

|   | 2.2 ADDRESSING MODE                       |    |

|   | 2.2.1 IMMEDIATE ADDRESSING MODE           |    |

|   | 2.2.2 DIRECTLY ADDRESSING MODE            |    |

|   | 2.2.3 INDIRECTLY ADDRESSING MODE          |    |

|   | 2.3 STACK OPERATION                       |    |

|   | 2.3.1 OVERVIEW                            |    |

|   | 2.3.2 STACK REGISTERS                     |    |

|   | 2.3.3 STACK OPERATION EXAMPLE             | 36 |

| 3 | RESET                                     |    |

|   | 3.1 OVERVIEW                                   |    |

|---|------------------------------------------------|----|

|   | 3.2 POWER ON RESET                             | 39 |

|   | 3.3 WATCHDOG RESET                             | 39 |

|   | 3.4 BROWN OUT RESET                            | 40 |

|   | 3.4.1 BROWN OUT DESCRIPTION                    | 40 |

|   | 3.4.2 THE SYSTEM OPERATING VOLTAGE DECSRIPTION | 41 |

|   | 3.4.3 BROWN OUT RESET IMPROVEMENT              | 42 |

|   | 3.5 EXTERNAL RESET                             | 43 |

|   | 3.6 EXTERNAL RESET CIRCUIT                     | 43 |

|   | 3.6.1 Simply RC Reset Circuit                  |    |

|   | 3.6.2 Diode & RC Reset Circuit                 | 44 |

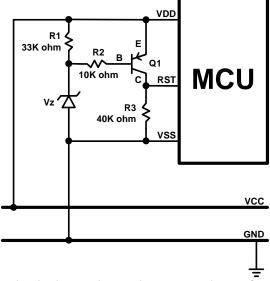

|   | 3.6.3 Zener Diode Reset Circuit                | 44 |

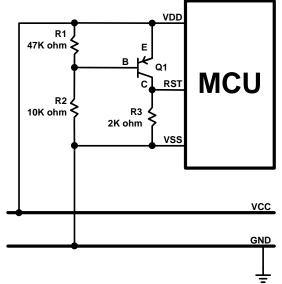

|   | 3.6.4 Voltage Bias Reset Circuit               |    |

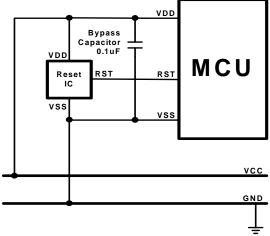

|   | 3.6.5 External Reset IC                        |    |

| 4 | SYSTEM CLOCK                                   | 46 |

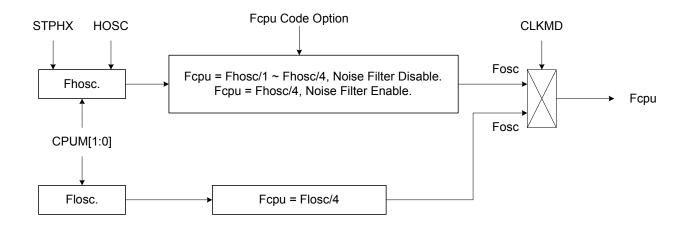

|   | 4.1 OVERVIEW                                   | 46 |

|   | 4.2 CLOCK BLOCK DIAGRAM                        | 46 |

|   | 4.3 OSCM REGISTER                              | 47 |

|   | 4.4 SYSTEM HIGH CLOCK                          | 48 |

|   | 4.4.1 INTERNAL HIGH RC                         | 48 |

|   | 4.5 SYSTEM LOW CLOCK                           | 48 |

|   | 4.5.1 SYSTEM CLOCK MEASUREMENT                 | 49 |

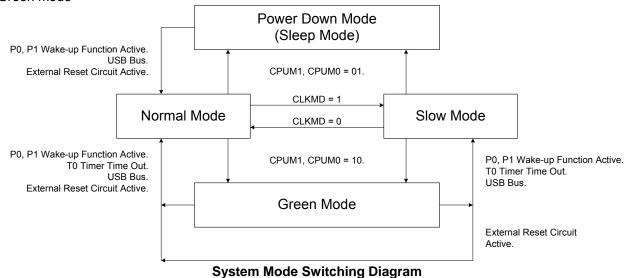

| 5 | SYSTEM OPERATION MODE                          | 50 |

|   | 5.1 OVERVIEW                                   | 50 |

|   | 5.2 SYSTEM MODE SWITCHING EXAMPLE              | 51 |

|   | 5.3 WAKEUP                                     | 53 |

|   | 5.3.1 OVERVIEW                                 | 53 |

|   | 5.3.2 WAKEUP TIME                              | 53 |

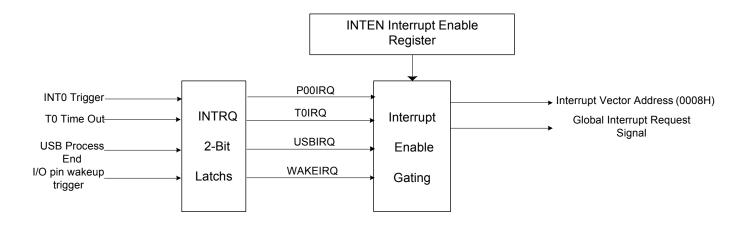

| 6 | INTERRUPT                                      | 54 |

|   | 6.1 OVERVIEW                                   | 54 |

|   | 6.2 INTEN INTERRUPT ENABLE REGISTER            | 55 |

|   | 6.3 INTRQ INTERRUPT REQUEST REGISTER           |    |

|   | 6.4 GIE GLOBAL INTERRUPT OPERATION             |    |

|   | 6.5 PUSH, POP ROUTINE                          | 56 |

|   | 6.6 INTO (P0.0) INTERRUPT OPERATION            | 57 |

|   | 6.7 T0 INTERRUPT OPERATION                     | 59 |

|   | 6.8 USB INTERRUPT OPERATION                    | 60 |

|   | 6.9 WAKEUP INTERRUPT OPERATION                 | 61 |

|    | 6.10 MULTI-INTERRUPT OPERATION                     | 62 |

|----|----------------------------------------------------|----|

| 7  | 7 I/O PORT                                         | 63 |

|    | 7.1 I/O PORT MODE                                  | 63 |

|    | 7.2 I/O PULL UP REGISTER                           | 64 |

|    | 7.3 I/O PORT DATA REGISTER                         | 65 |

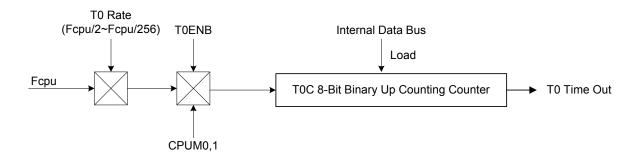

| 8  | 3 TIMERS                                           | 66 |

|    | 8.1 WATCHDOG TIMER                                 | 66 |

|    | 8.2 TIMER 0 (T0)                                   | 68 |

|    | 8.2.1 OVERVIEW                                     | 68 |

|    | 8.2.2 TOM MODE REGISTER                            | 68 |

|    | 8.2.3 TOC COUNTING REGISTER                        | 69 |

|    | 8.2.4 TO TIMER OPERATION SEQUENCE                  | 70 |

| 9  | UNIVERSAL SERIAL BUS (USB)                         | 71 |

|    | 9.1 OVERVIEW                                       | 71 |

|    | 9.2 USB MACHINE                                    | 71 |

|    | 9.3 USB INTERRUPT                                  | 72 |

|    | 9.4 USB ENUMERATION                                | 72 |

|    | 9.5 USB REGISTERS                                  | 73 |

|    | 9.5.1 USB DEVICE ADDRESS REGISTER                  |    |

|    | 9.5.2 USB STATUS REGISTER                          |    |

|    | 9.5.3 USB DATA COUNT REGISTER                      |    |

|    | 9.5.4 USB ENABLE CONTROL REGISTER                  |    |

|    | 9.5.5 USB endpoint's ACK handshaking flag REGISTER |    |

|    | 9.5.6 USB ENDPOINT 0 ENABLE REGISTER               |    |

|    | 9.5.7 USB ENDPOINT 1 ENABLE REGISTER               |    |

|    | 9.5.8 USB ENDPOINT 2 ENABLE REGISTER               |    |

|    | 9.5.9 USB DATA POINTER REGISTER                    |    |

|    | 9.5.10 USB DATA READ/WRITE REGISTER                |    |

|    | 9.5.11 UPID REGISTER                               |    |

|    | 9.5.12 ENDPOINT TOGGLE BIT CONTROL REGISTER        |    |

| 1( | 10 INSTRUCTION TABLE                               | 81 |

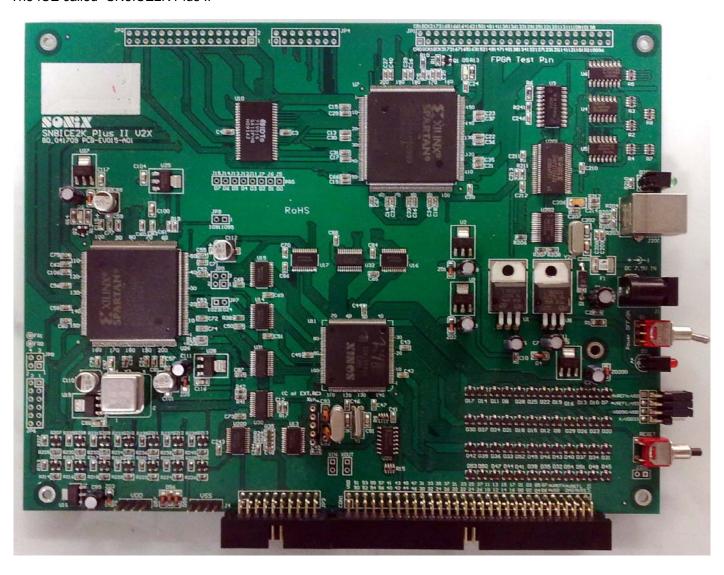

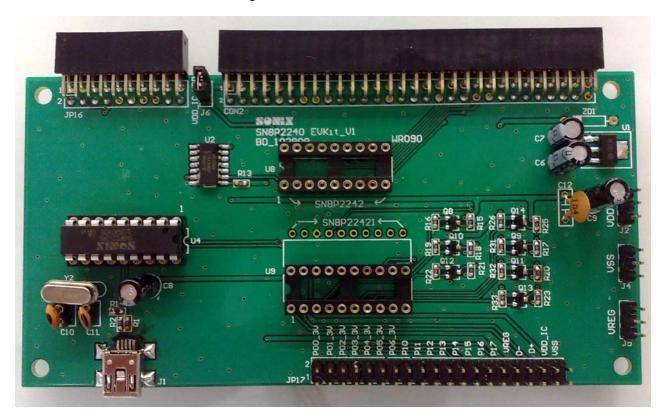

| 11 | 1 DEVELOPMENT TOOL                                 | 82 |

|    | 11.1 ICE (IN CIRCUIT EMULATION)                    |    |

|    | 11.2 SN8P2240 EV-Kit                               | 83 |

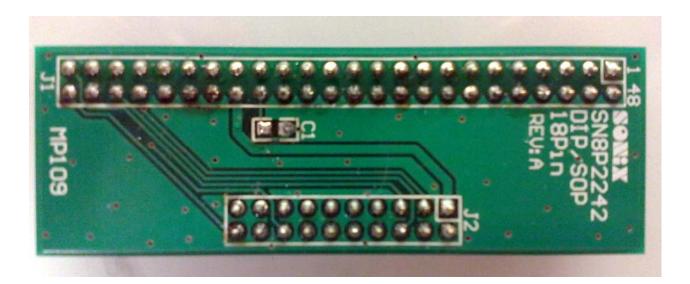

|    | 11.3 SN8P2240 Transition Board                     | 84 |

| 12 | 2 ELECTRICAL CHARACTERISTIC                        | 85 |

|      | ABSOLUTE MAXIMUM RATING         |    |

|------|---------------------------------|----|

| 12.2 | 2 ELECTRICAL CHARACTERISTIC     | 85 |

| 13   | OTP ROM PROGRAMMING PIN         | 86 |

| 14   | PACKAGE INFORMATION             | 87 |

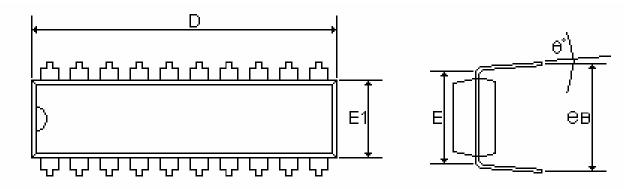

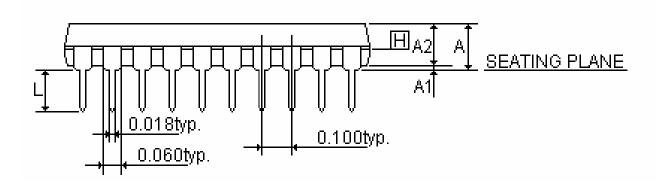

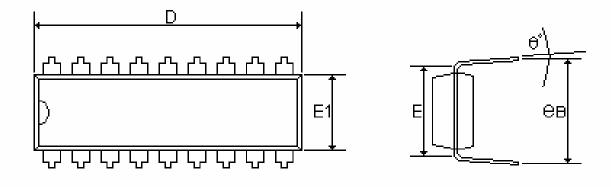

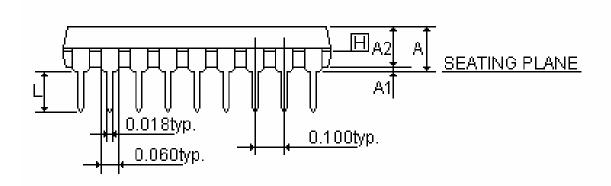

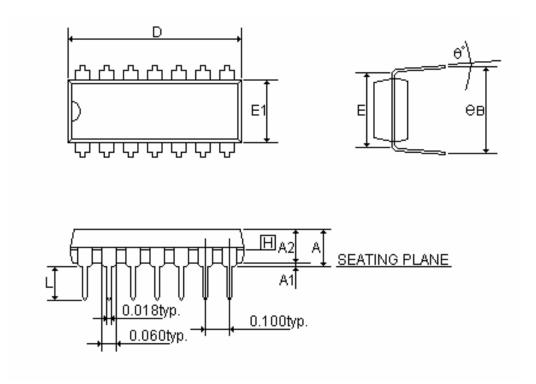

| 14.1 | P-DIP 20 PIN                    | 87 |

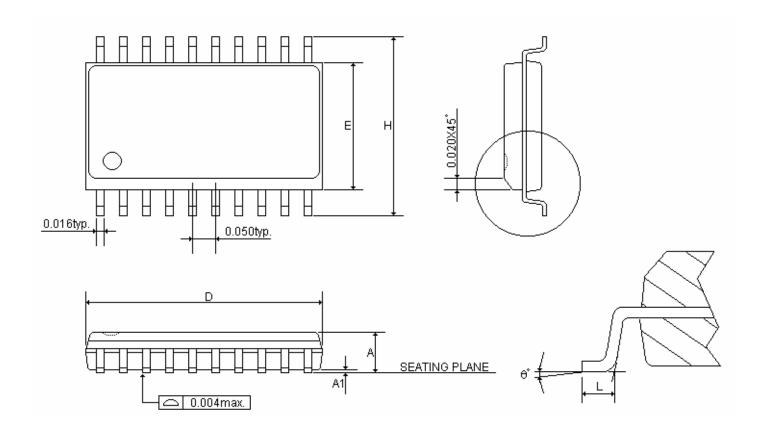

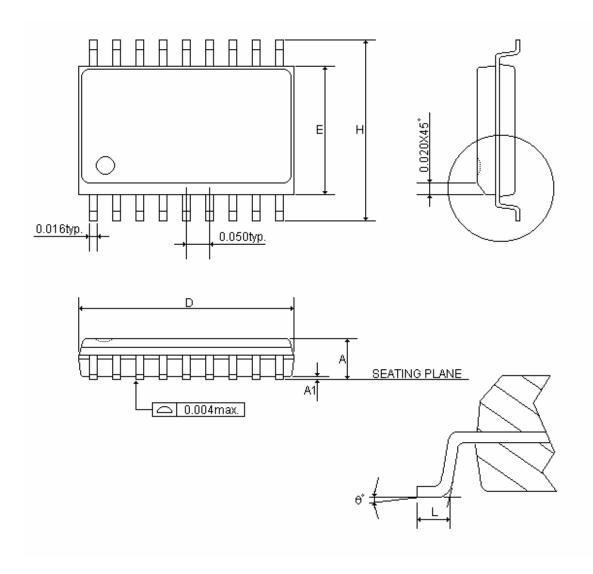

| 14.2 | 2 SOP 20 PIN                    | 88 |

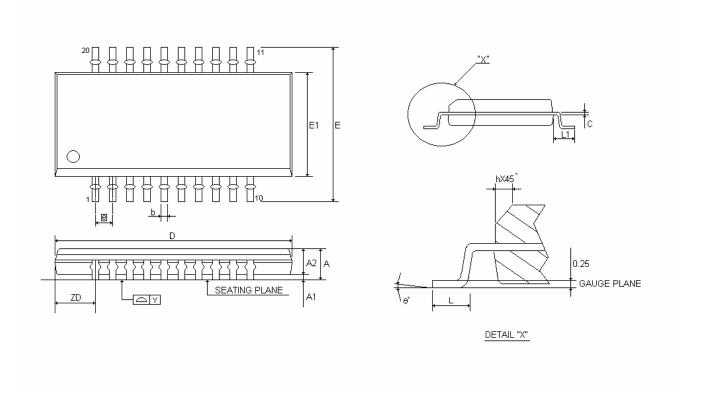

| 14.3 | 3 SSOP 20 PIN                   | 89 |

| 14.4 | 4 P-DIP 18 PIN                  | 90 |

| 14.5 | 5 SOP 18 PIN                    | 91 |

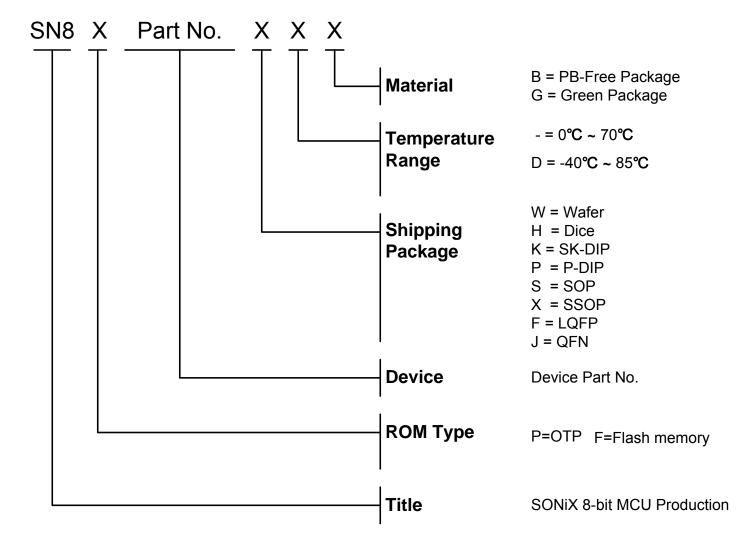

| 15   | MARKING DEFINITION              | 93 |

| 15.1 | INTRODUCTION                    | 93 |

| 15.2 | 2 MARKING INDETIFICATION SYSTEM | 93 |

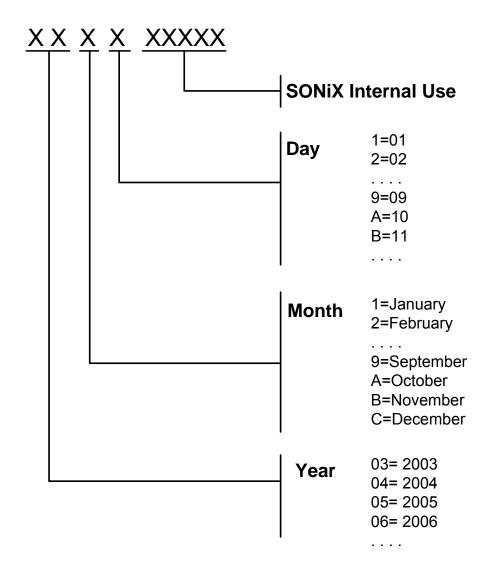

| 15.3 | 3 MARKING EXAMPLE               | 94 |

| 15.4 | DATECODE SYSTEM                 | 94 |

Page 6

# PRODUCT OVERVIEW

### 1.1 FEATURES

**Memory configuration**

OTP ROM size: 3K x 16 bits. RAM size: 128 x 8 bits.

8 levels stack buffer

♦ I/O pin configuration

Bi-directional: P0, P1

Wake-up: P0/P1 level change Pull-up resistors: P0, P1

♦ Low Speed USB 2.0

Conforms to USB Specification, Version 2.0 3.3V regulator output for USB D- pin internal 1.5k ohm pull-up resistor. Integrated USB transceiver. Supports 1 Low speed USB device address and

1 control endpoint has 8 bytes FIFO 2 interrupt endpoints, each has 8 bytes FIFO

Powerful instructions

Instruction cycle controlled by code option.

Instruction length is one word.

Most of instructions are one cycle only.

Maximum instruction cycle is two.

All ROM area JMP instruction.

All ROM area CALL address instruction.

All ROM area lookup table function (MOVC)

♦ 4 interrupt sources

3 internal interrupts: T0, USB, Wakeup

1 external interrupts: INT0

One 8 bits timer counter T0

On chip watchdog timer

♦ Two system clocks

Internal high clock: 6MHz

Internal low clock: RC type 32KHz@5V

Four operating modes

Normal mode: Both high and low clock active

Slow mode: Low clock only

Sleep mode: Both high and low clock stop Green mode: Periodical wakeup by timer

Package (Chip form support)

DIP/SOP/SSOP 20 PIN DIP/SOP 18 PIN DIP 14 PIN

#### Features Selection Table

| CHIP      | CHIP ROM RAM | A STACK              | TIMER | USB | USB I/O | WAKE-UP | PACKAGE |              |

|-----------|--------------|----------------------|-------|-----|---------|---------|---------|--------------|

| СПР       | KOW          | I RAM STACK TO USB I | STACK | 1/0 | PIN NO. | PACKAGE |         |              |

| SN8P22421 | 3K*16        | 128*8                | 8     | ٧   | V       | 15      | 15      | DIP/SOP/SSOP |

| SN8P2242  | 3K*16        | 128*8                | 8     | ٧   | ٧       | 13      | 13      | DIP/SOP      |

| SN8P2241  | 3K*16        | 128*8                | 8     | ٧   | ٧       | 9       | 9       | DIP          |

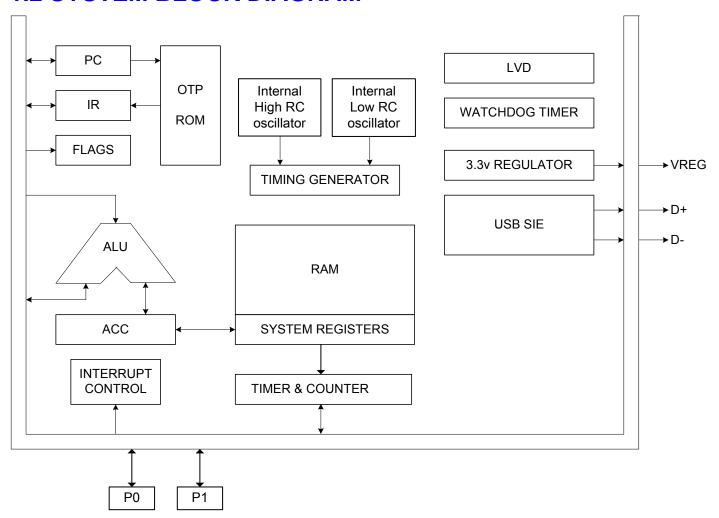

## 1.2 SYSTEM BLOCK DIAGRAM

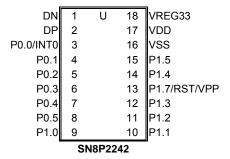

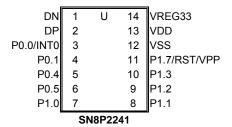

## 1.3 PIN ASSIGNMENT

SN8P22421P/S/X (DIP/SOP/SSOP)

| DN        | 1  | U | 20 | VREG33       |  |

|-----------|----|---|----|--------------|--|

| DP        | 2  |   | 19 | VDD          |  |

| P0.0/INT0 | 3  |   | 18 | VSS          |  |

| P0.1      | 4  |   | 17 | P1.6         |  |

| P0.2      | 5  |   | 16 | P1.5         |  |

| P0.3      | 6  |   | 15 | P1.4         |  |

| P0.4      | 7  |   | 14 | P1.7/RST/VPP |  |

| P0.5      | 8  |   | 13 | P1.3         |  |

| P0.6      | 9  |   | 12 | P1.2         |  |

| P1.0      | 10 |   | 11 | P1.1         |  |

| SN8P22421 |    |   |    |              |  |

SN8P2242P/S (DIP/SOP)

**SN8P2241P (DIP)**

## 1.4 PIN DESCRIPTIONS

| PIN NAME     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                       |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD, VSS     | Р    | Power supply input pins for digital circuit.                                                                                                                                                                                                                      |

| P0.0/INT0    | I/O  | P0.0: Port 0.0 bi-direction pin. Schmitt trigger structure and built-in pull-up resisters as input mode. Built wakeup function. INT0: External interrupt 0 input pin.                                                                                             |

| P0[6:1]      | I/O  | P0: Port 0 bi-direction pin. Schmitt trigger structure and built-in pull-up resisters as input mode. Built wakeup function.                                                                                                                                       |

| P1[6:0]      | I/O  | P1: Port 1 bi-direction pin. Schmitt trigger structure and built-in pull-up resisters as input mode. Built wakeup function.                                                                                                                                       |

| P1.7/RST/VPP | I, P | RST is system external reset input pin under Ext_RST mode. Schmitt trigger structure, active "low", normal stay to "high". P1.7 is input only pin without pull-up resistor under P1.7 mode. Built wakeup function. OTP 12.3V power input pin in programming mode. |

| VREG33       | 0    | 3.3V voltage output from USB 3.3V regulator.                                                                                                                                                                                                                      |

| D+, D-       | I/O  | USB differential data line.                                                                                                                                                                                                                                       |

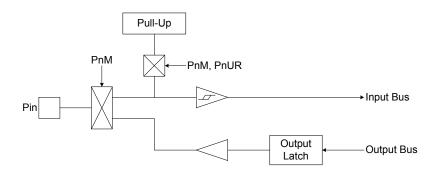

## 1.5 PIN CIRCUIT DIAGRAMS

#### Port 0, 1 structures:

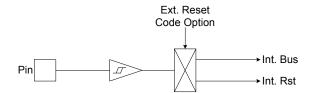

#### Pin RST structure:

# 2 CENTRAL PROCESSOR UNIT (CPU)

## 2.1 MEMORY MAP

## 2.1.1 PROGRAM MEMORY (ROM)

#### 3K words ROM

| 0000H           | Reset vector         | User reset vector Jump to user start address |

|-----------------|----------------------|----------------------------------------------|

| 0001H           |                      | •                                            |

|                 | General purpose area |                                              |

| 0007H           |                      |                                              |

| H8000           | Interrupt vector     | User interrupt vector                        |

| 0009H           |                      | User program                                 |

|                 |                      |                                              |

| 000FH           |                      |                                              |

| 001111<br>0010H |                      |                                              |

| 0011H           | General purpose area |                                              |

|                 |                      |                                              |

| •               |                      |                                              |

| •               |                      |                                              |

| •               |                      | End of user program                          |

| BFCH            |                      |                                              |

|                 | Reserved             |                                              |

| DEEU            | 113331133            |                                              |

| BFFH            |                      |                                              |

**ROM**

#### 2.1.1.1 RESET VECTOR (0000H)

A one-word vector address area is used to execute system reset.

- Power On Reset (NT0=1, NPD=0).

- Watchdog Reset (NT0=0, NPD=0).

- External Reset (NT0=1, NPD=1).

After power on reset, external reset or watchdog timer overflow reset, then the chip will restart the program from address 0000h and all system registers will be set as default values. It is easy to know reset status from NT0, NPD flags of PFLAG register. The following example shows the way to define the reset vector in the program memory.

Example: Defining Reset Vector

ORG 0 ; 0000H

JMP START ; Jump to user program address.

. . .

ORG 10H

**START:** ; 0010H, The head of user program.

... ; User program

• • •

ENDP ; End of program

#### **2.1.1.2 INTERRUPT VECTOR (0008H)**

A 1-word vector address area is used to execute interrupt request. If any interrupt service executes, the program counter (PC) value is stored in stack buffer and jump to 0008h of program memory to execute the vectored interrupt. Users have to define the interrupt vector. The following example shows the way to define the interrupt vector in the program memory.

Note:"PUSH", "POP" instructions save and load ACC/PFLAG without (NT0, NPD). PUSH/POP buffer is a unique buffer and only one level.

> Example: Defining Interrupt Vector. The interrupt service routine is following ORG 8.

.CODE

ORG 0 ; 0000H

JMP START ; Jump to user program address.

• • •

ORG 8 ; Interrupt vector.

PUSH ; Save ACC and PFLAG register to buffers.

• • •

POP ; Load ACC and PFLAG register from buffers.

**RETI** ; End of interrupt service routine

•••

START: ; The head of user program.

... ; User program

JMP START ; End of user program

. . .

ENDP ; End of program

Example: Defining Interrupt Vector. The interrupt service routine is following user program.

.CODE

ORG 0 ; 0000H

JMP START ; Jump to user program address.

ORG 8 ; Interrupt vector.

JMP MY\_IRQ ; 0008H, Jump to interrupt service routine address.

ORG 10H

START: ; 0010H, The head of user program.

; User program.

•••

JMP START ; End of user program.

MY\_IRQ: ;The head of interrupt service routine.

PUSH ; Save ACC and PFLAG register to buffers.

• • •

POP ; Load ACC and PFLAG register from buffers.

RETI ; End of interrupt service routine.

...

ENDP ; End of program.

- \* Note: It is easy to understand the rules of SONIX program from demo programs given above. These points are as following:

- 1. The address 0000H is a "JMP" instruction to make the program starts from the beginning.

- 2. The address 0008H is interrupt vector.

- 3. User's program is a loop routine for main purpose application.

#### 2.1.1.3 LOOK-UP TABLE DESCRIPTION

In the ROM's data lookup function, Y/H register is pointed to middle byte address (bit 8~bit 15) and Z/L register is pointed to low byte address (bit 0~bit 7) of ROM. After MOVC instruction executed, the low-byte data will be stored in ACC and high-byte data stored in R register.

> Example: To look up the ROM data located "TABLE1".

| B0MOV<br>B0MOV<br>MOVC       | Y, #TABLE1\$M<br>Z, #TABLE1\$L | ; To set lookup table1's middle address<br>; To set lookup table1's low address.<br>; To lookup data, R = 00H, ACC = 35H |

|------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| INCMS<br>JMP<br>INCMS<br>NOP | Z<br>@F<br>Y                   | ; Increment the index address for next address.<br>; Z+1<br>; Z is not overflow.<br>; Z overflow (FFH → 00), → Y=Y+1     |

| 1401/0                       |                                | '- · · · · · · · · · ·                                                                                                   |

@@: MOVC ; To lookup data, R = 51H, ACC = 05H. ;

TABLE1: DW 0035H ; To define a word (16 bits) data.

TABLE1: DW 0035H DW 5105H DW 2012H

Note: The Y register will not increase automatically when Z register crosses boundary from 0xFF to 0x00. Therefore, user must take care such situation to avoid loop-up table errors. If Z register overflows, Y register must be added one. The following INC\_YZ macro shows a simple method to process Y and Z registers automatically.

> Example: INC\_YZ macro.

| INC_YZ  | MACRO<br>INCMS<br>JMP | Z<br>@F | ; Z+1<br>; Not overflow |

|---------|-----------------------|---------|-------------------------|

| <b></b> | INCMS<br>NOP          | Υ       | ; Y+1<br>; Not overflow |

| @@:     | ENDM                  |         |                         |

Example: Modify above example by "INC\_YZ" macro.

B0MOV Y, #TABLE1\$M ; To set lookup table1's middle address B0MOV Z, #TABLE1\$L ; To set lookup table1's low address. MOVC ; To lookup data, R = 00H, ACC = 35H

INC\_YZ ; Increment the index address for next address.

@@: MOVC ; To lookup data, R = 51H, ACC = 05H.

TABLE1: DW 0035H ; To define a word (16 bits) data.

DW 5105H DW 2012H

• • •

The other example of loop-up table is to add Y or Z index register by accumulator. Please be careful if "carry" happen.

Example: Increase Y and Z register by B0ADD/ADD instruction.

B0MOV Y, #TABLE1\$M ; To set lookup table's middle address. B0MOV Z, #TABLE1\$L ; To set lookup table's low address.

B0MOV A, BUF ; Z = Z + BUF. B0ADD Z, A

B0BTS1 FC ; Check the carry flag.

JMP GETDATA ; FC = 0 INCMS Y ; FC = 1. Y+1.

NOP GETDATA:

MOVC ; To lookup data. If BUF = 0, data is 0x0035

; If BUF = 1, data is 0x5105 ; If BUF = 2, data is 0x2012

• • •

TABLE1: DW 0035H ; To define a word (16 bits) data.

DW 5105H DW 2012H

...

#### 2.1.1.4 JUMP TABLE DESCRIPTION

The jump table operation is one of multi-address jumping function. Add low-byte program counter (PCL) and ACC value to get one new PCL. If PCL is overflow after PCL+ACC, PCH adds one automatically. The new program counter (PC) points to a series jump instructions as a listing table. It is easy to make a multi-jump program depends on the value of the accumulator (A).

Note: PCH only support PC up counting result and doesn't support PC down counting. When PCL is carry after PCL+ACC, PCH adds one automatically. If PCL borrow after PCL-ACC, PCH keeps value and not change.

#### > Example: Jump table.

| ORG        | 0X0100             | ; The jump table is from the head of the ROM boundary    |

|------------|--------------------|----------------------------------------------------------|

| B0ADD      | PCL, A             | ; PCL = PCL + ACC, PCH + 1 when PCL overflow occurs.     |

| JMP<br>JMP | A0POINT<br>A1POINT | ; ACC = 0, jump to A0POINT<br>; ACC = 1, jump to A1POINT |

| JMP        | A2POINT            | ; ACC = 2, jump to A2POINT                               |

| JMP        | A3POINT            | ; ACC = 3, jump to A3POINT                               |

SONIX provides a macro for safe jump table function. This macro will check the ROM boundary and move the jump table to the right position automatically. The side effect of this macro maybe wastes some ROM size.

Example: If "jump table" crosses over ROM boundary will cause errors.

```

@JMP_A MACRO VAL

IF (($+1)!& 0XFF00)!!= (($+(VAL))!& 0XFF00)

JMP ($|0XFF)

ORG ($|0XFF)

ENDIF

ADD PCL, A

ENDM

```

Note: "VAL" is the number of the jump table listing number.

#### Example: "@JMP\_A" application in SONIX macro file called "MACRO3.H".

| B0MOV  | A, BUF0 | ; "BUF0" is from 0 to 4.                        |

|--------|---------|-------------------------------------------------|

| @JMP_A | 5       | ; The number of the jump table listing is five. |

| JMP    | A0POINT | ; ACC = 0, jump to A0POINT                      |

| JMP    | A1POINT | ; ACC = 1, jump to A1POINT                      |

| JMP    | A2POINT | ; ACC = 2, jump to A2POINT                      |

| JMP    | A3POINT | ; ACC = 3, jump to A3POINT                      |

| JMP    | A4POINT | ; ACC = 4, jump to A4POINT                      |

|        |         |                                                 |

If the jump table position is across a ROM boundary (0x00FF~0x0100), the "@JMP\_A" macro will adjust the jump table routine begin from next RAM boundary (0x0100).

#### > Example: "@JMP\_A" operation.

#### ; Before compiling program.

| ROM address |        |         |                                                 |

|-------------|--------|---------|-------------------------------------------------|

|             | B0MOV  | A, BUF0 | ; "BUF0" is from 0 to 4.                        |

|             | @JMP_A | 5       | ; The number of the jump table listing is five. |

| 0X00FD      | JMP _  | A0POINT | ; ACC = 0, jump to A0POINT                      |

| 0X00FE      | JMP    | A1POINT | ; ACC = 1, jump to A1POINT                      |

| 0X00FF      | JMP    | A2POINT | ; ACC = 2, jump to A2POINT                      |

| 0X0100      | JMP    | A3POINT | ; ACC = 3, jump to A3POINT                      |

| 0X0101      | JMP    | A4POINT | ; ACC = 4, jump to A4POINT                      |

|             |        |         |                                                 |

#### ; After compiling program.

#### **ROM** address

|        | B0MOV  | A, BUF0 | ; "BUF0" is from 0 to 4.                        |

|--------|--------|---------|-------------------------------------------------|

|        | @JMP_A | 5       | ; The number of the jump table listing is five. |

| 0X0100 | JMP    | A0POINT | ; ACC = 0, jump to A0POINT                      |

| 0X0101 | JMP    | A1POINT | ; ACC = 1, jump to A1POINT                      |

| 0X0102 | JMP    | A2POINT | ; ACC = 2, jump to A2POINT                      |

| 0X0103 | JMP    | A3POINT | ; ACC = 3, jump to A3POINT                      |

| 0X0104 | JMP    | A4POINT | ; ACC = 4, jump to A4POINT                      |

#### 2.1.1.5 CHECKSUM CALCULATION

The last ROM addresses are reserved area. User should avoid these addresses (last address) when calculate the Checksum value.

Example: The demo program shows how to calculated Checksum from 00H to the end of user's code.

|                | MOV<br>B0MOV<br>MOV<br>B0MOV<br>CLR<br>CLR        | A,#END_USER_CODE\$L<br>END_ADDR1, A<br>A,#END_USER_CODE\$M<br>END_ADDR2, A<br>Y<br>Z | ; Save low end address to end_addr1<br>; Save middle end address to end_addr2<br>; Set Y to 00H<br>; Set Z to 00H                                                                                  |

|----------------|---------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| @@:<br>AAA:    | MOVC<br>B0BSET<br>ADD<br>MOV<br>ADC<br>JMP        | FC<br>DATA1, A<br>A, R<br>DATA2, A<br>END_CHECK                                      | ; Clear C flag<br>; Add A to Data1<br>; Add R to Data2<br>; Check if the YZ address = the end of code                                                                                              |

|                | INCMS<br>JMP<br>JMP                               | Z<br>@B<br>Y_ADD_1                                                                   | ; Z=Z+1<br>; If Z != 00H calculate to next address<br>; If Z = 00H increase Y                                                                                                                      |

| END_CHECK:     | MOV<br>CMPRS<br>JMP<br>MOV<br>CMPRS<br>JMP<br>JMP | A, END_ADDR1<br>A, Z<br>AAA<br>A, END_ADDR2<br>A, Y<br>AAA<br>CHECKSUM_END           | ; Check if Z = low end address<br>; If Not jump to checksum calculate<br>; If Yes, check if Y = middle end address<br>; If Not jump to checksum calculate<br>; If Yes checksum calculated is done. |

| Y_ADD_1:       | INCMS<br>NOP                                      | Υ                                                                                    | ; Increase Y                                                                                                                                                                                       |

| CHECKSUM_END:  | JMP                                               | @B                                                                                   | ; Jump to checksum calculate                                                                                                                                                                       |

| END_USER_CODE: | <br>:                                             |                                                                                      | ; Label of program end                                                                                                                                                                             |

## 2.1.2 CODE OPTION TABLE

| Code Option | Content   | Function Description                                                           |  |  |  |

|-------------|-----------|--------------------------------------------------------------------------------|--|--|--|

|             | Always_On | Watchdog timer is always on enable even in power down and green mode.          |  |  |  |

| Watch_Dog   | Enable    | Enable watchdog timer. Watchdog timer stops in power down mode and green mode. |  |  |  |

|             | Disable   | Disable Watchdog function.                                                     |  |  |  |

|             | Fhosc/1   | Instruction cycle is 6 MHz clock.                                              |  |  |  |

| Fcpu        | Fhosc/2   | Instruction cycle is 3 MHz clock.                                              |  |  |  |

|             | Fhosc/4   | Instruction cycle is 1.5 MHz clock.                                            |  |  |  |

| Reset Pin   | Reset     | Enable External reset pin without pull up resistor.                            |  |  |  |

| Keset_Fill  | P17       | Enable P1.7 I/O function.                                                      |  |  |  |

| Det Longth  | No        | No external reset de-bounce time.                                              |  |  |  |

| Rst_Length  | 128*ILRC  | External reset de-bounce time = 128*ILRC.                                      |  |  |  |

| Security    | Enable    | Enable ROM code Security function.                                             |  |  |  |

| Security    | Disable   | Disable ROM code Security function.                                            |  |  |  |

Note: Fcpu code option is only available for High Clock. Fcpu of slow mode is Flosc/4.

## 2.1.3 DATA MEMORY (RAM)

#### ☞ 128 X 8-bit RAM

| Address | RAM location         |                         |

|---------|----------------------|-------------------------|

| 000h    |                      | BANK 0                  |

| "       |                      |                         |

| "       |                      |                         |

| 44      | General purpose area |                         |

| "       |                      |                         |

| ű       |                      |                         |

| 07Fh    |                      |                         |

| 080h    |                      | 80h~FFh of Bank 0 store |

| "       |                      | system registers (128   |

| "       |                      | bytes).                 |

| "       | System register      | ,                       |

| "       |                      |                         |

| ű       |                      |                         |

| 0FFh    | End of bank 0 area   | 1                       |

#### 32 x 8-bit RAM for USB DATA FIFO

##

#### 2.1.4 SYSTEM REGISTER

#### 2.1.4.1 SYSTEM REGISTER TABLE

|   | 0     | 1           | 2              | 3              | 4          | 5          | 6          | 7     | 8     | 9     | Α     | В     | С       | D     | Е     | F     |

|---|-------|-------------|----------------|----------------|------------|------------|------------|-------|-------|-------|-------|-------|---------|-------|-------|-------|

| 8 | -     | -           | R              | Z              | Y          | -          | PFLAG      | -     | -     | -     | -     | -     | -       | -     | -     | -     |

| 9 | UDA   | USTAT<br>US | EP0OUT<br>_CNT | USB_IN<br>T_EN | EP<br>_ACK | -          | UE0R       | UE1R  | UE2R  | ı     | ı     | ı     | ı       | ı     | ı     | -     |

| Α | -     | -           | -              | UDP0_L         | UDP0_<br>H | UDR0_<br>R | UDR0_<br>W | -     | -     | -     | -     | UPID  | UToggle | -     | 1     | -     |

| В | IHRCU | IHRCL       | -              | -              | 1          | -          | 1          | -     | P0M   | 1     | -     | 1     | 1       | -     | -     | PEDGE |

| С | ı     | P1M         | -              | -              | ı          | -          | ı          | -     | INTRQ | INTEN | OSCM  | ı     | WDTR    | ı     | PCL   | PCH   |

| D | P0    | P1          | -              | -              | -          | -          | -          | -     | TOM   | T0C   | -     | -     | -       | -     | -     | STKP  |

| Ε | P0UR  | P1UR        | -              | -              | -          | -          | 1          | @YZ   | -     | 1     | -     | 1     | -       | -     | -     | -     |

| F | STK7L | STK7H       | STK6L          | STK6H          | STK5L      | STK5H      | STK4L      | STK4H | STK3L | STK3H | STK2L | STK2H | STK1L   | STK1H | STK0L | STK0H |

#### 2.1.4.2 SYSTEM REGISTER DESCRIPTION

R = Working register and ROM look-up data buffer.

PFLAG = ROM page and special flag register.

UDA = USB control register.

UDP0 = USB FIFO address pointer.

UDR0\_W = USB FIFO write data buffer by UDP0 point to.

EP\_ACK = Endpoint ACK flag register.

UToggle = USB endpoint toggle bit control register.

USTATUS = USB status register.

EPOOUT\_CNT = USB endpoint 0 OUT token data byte counter

PnM = Port n input/output mode register.

INTRQ = Interrupt request register.

OSCM = Oscillator mode register.

Pn = Port n data buffer.

TnC = Tn counting register. n = 0

PnUR = Port n pull-up resister control register.

Y, Z = Working, @YZ and ROM addressing register.

UE0R~UE2R = Endpoint 0~2 control registers.

UDR0\_R = USB FIFO read data buffer by UDP0 point to.

UDR0\_W = USB FIFO write data buffer by UDP1 point to.

UPID = USB bus control register.

USB\_INT\_EN = USB interrupt enable/disable control register.

PEDGE = P0.0, P0.1 edge direction register.

INTEN = Interrupt enable register.

WDTR = Watchdog timer clear register.

PCH, PCL = Program counter.

TnM = Tn mode register. n = 0

STKP = Stack pointer buffer.

@YZ = RAM YZ indirect addressing index pointer.

STK0~STK7 = Stack 0 ~ stack 7 buffer.

#### 2.1.4.3 BIT DEFINITION of SYSTEM REGISTER

| Address      | Bit7         | Bit6             | Bit5         | Bit4            | Bit3            | Bit2            | Bit1            | Bit0              | R/W        | Remarks        |

|--------------|--------------|------------------|--------------|-----------------|-----------------|-----------------|-----------------|-------------------|------------|----------------|

| 082H         | RBIT7        | RBIT6            | RBIT5        | RBIT4           | RBIT3           | RBIT2           | RBIT1           | RBIT0             | R/W        | R              |

| 083H         | ZBIT7        | ZBIT6            | ZBIT5        | ZBIT4           | ZBIT3           | ZBIT2           | ZBIT1           | ZBIT0             | R/W        | Z              |

| 084H         | YBIT7        | YBIT6            | YBIT5        | YBIT4           | YBIT3           | YBIT2           | YBIT1           | YBIT0             | R/W        | Y              |

| 086H         | NT0          | NPD              |              |                 |                 | С               | DC              | Z                 | R/W        | PFLAG          |

| 090H         | UDE          | UDA6             | UDA5         | UDA4            | UDA3            | UDA2            | UDA1            | UDA0              | R/W        | UDA            |

| 091H         | IDLE_ER<br>R | BIT_TIME_<br>ERR | TX_ERR       | BUS_RST         | SUSPEND         | EP0_SET<br>UP   | EP0_IN          | EP0_OUT           | R/W        | USTATUS        |

| 092H         |              |                  |              | UEP0OC4         | UEP0OC3         | UEP0OC2         | UEP0OC1         | UEP0OC0           | R/W        | EP0OUT_CNT     |

| 093H         | REG_EN       | DN_PU_E<br>N     |              |                 |                 |                 |                 |                   | R/W        | USB_INT_EN     |

| 094H         |              |                  |              |                 |                 |                 | EP2_ACK         | EP1_ACK           | R/W        | EP_ACK         |

| 096H         | UE0E         | UE0M1            | UE0M0        |                 | UE0C3           | UE0C2           | UE0C1           | UE0C0             | R/W        | UE0R           |

| 097H         | UE1E         | UE1M1            | UE1M0        | UE1D            | UE1C3           | UE1C2           | UE1C1           | UE1C0             | R/W        | UE1R           |

| 098H         | UE2E         | UE2M1            | UE2M0        | UE2D            | UE2C3           | UE2C2           | UE2C1           | UE2C0             | R/W        | UE2R           |

| 0A3H         | UDP07        | UDP06            | UDP05        | UDP04           | UDP03           | UDP02           | UDP01           | UDP00             | R/W        | UDP0_L         |

| 0A4H         | WE0          | RD0              |              |                 |                 |                 |                 |                   | R/W        | UDP0_H         |

| 0A5H         | UDR0_R7      | UDR0_R6          | UDR0_R5      | UDR0_R4         | UDR0_R3         | UDR0_R2         | UDR0_R1         | UDR0_R0           | R/W        | UDR0_R         |

| 0A6H         | UDR0_W7      | UDR0_W6          | UDR0_W5      | UDR0_W4         | UDR0_W3         |                 | UDR0_W1         | UDR0_W0           | R/W        | UDR0_W         |

| 0ABH         |              |                  |              | CRC_ERR         | PKT_ERR         | UBDE            | DDP             | DDN               | R/W        | UPID           |

| 0ACH         |              |                  |              |                 |                 |                 | EP2_DATA<br>0/1 | EP1_DATA<br>0/1   | R/W        | Utoggle        |

| 0B0H         |              |                  |              |                 |                 |                 |                 | EP0_IN_ST<br>ALL  | R/W        | IHRCU          |

| 0B1H         |              |                  |              |                 |                 |                 |                 | EP0_OUT_<br>STALL | R/W        | IHRCL          |

| 0B8H         |              | P06M             | P05M         | P04M            | P03M            | P02M            | P01M            | P00M              | R/W        | P0M            |

| 0BFH         |              |                  |              |                 |                 |                 | P00G1           | P00G0             | R/W        | PEDGE          |

| 0C1H         |              | P16M             | P15M         | P14M            | P13M            | P12M            | P11M            | P10M              | R/W        | P1M            |

| 0C8H         |              | USBIRQ           |              | T0IRQ           |                 | WAKEIRQ         |                 | P00IRQ            | R/W        | INTRQ          |

| 0C9H         |              | USBIEN           |              | T0IEN           |                 | WAKEIEN         |                 | P00IEN            | R/W        | INTEN          |

| 0CAH         |              |                  |              | CPUM1           | CPUM0           | CLKMD           | STPHX           |                   | R/W        | OSCM           |

| 0CCH         | WDTR7        | WDTR6            | WDTR5        | WDTR4           | WDTR3           | WDTR2           | WDTR1           | WDTR0             | W          | WDTR           |

| 0CEH         | PC7          | PC6              | PC5          | PC4             | PC3             | PC2             | PC1             | PC0               | R/W        | PCL            |

| 0CFH         |              |                  |              | PC12            | PC11            | PC10            | PC9             | PC8               | R/W        | PCH            |

| 0D0H         |              | P06              | P05          | P04             | P03             | P02             | P01             | P00               | R/W        | P0             |

| 0D1H         | P17          | P16              | P15          | P14             | P13             | P12             | P11             | P10               | R/W        | P1             |

| 0D8H         | T0ENB        | T0rate2          | T0rate1      | T0rate0         | T000            | T000            | T004            | T000              | R/W        | TOM            |

| 0D9H<br>0DFH | T0C7<br>GIE  | T0C6             | T0C5         | T0C4            | T0C3            | T0C2<br>STKPB2  | T0C1<br>STKPB1  | T0C0<br>STKPB0    | R/W<br>R/W | T0C<br>STKP    |

|              | GIL          | DOCD             | DOED         | D04D            | DOOD            |                 |                 |                   |            |                |

| 0E0H<br>0E1H |              | P06R<br>P16R     | P05R<br>P15R | P04R<br>P14R    | P03R<br>P13R    | P02R<br>P12R    | P01R<br>P11R    | P00R<br>P10R      | W          | P0UR<br>P1UR   |

| 0E7H         | @YZ7         | @YZ6             | @YZ5         | @YZ4            | @YZ3            | @YZ2            | @YZ1            | @YZ0              | R/W        | @YZ            |

|              |              |                  |              |                 |                 | <u> </u>        |                 | <u> </u>          | R/W        | STK7L          |

| 0F0H         | S7PC7        | S7PC6            | S7PC5        | S7PC4           | S7PC3           | S7PC2           | S7PC1           | S7PC0             |            |                |

| 0F1H<br>0F2H | S6PC7        | S6PC6            | S6PC5        | S7PC12<br>S6PC4 | S7PC11<br>S6PC3 | S7PC10<br>S6PC2 | S7PC9<br>S6PC1  | S7PC8<br>S6PC0    | R/W<br>R/W | STK7H<br>STK6L |

| 0F2H         | 30501        | 30700            | 30703        | S6PC12          | S6PC11          | S6PC2<br>S6PC10 | S6PC9           | S6PC0<br>S6PC8    | R/W        | STK6H          |

| 0F4H         | S5PC7        | S5PC6            | S5PC5        | S5PC4           | S5PC3           | S5PC2           | S5PC1           | S5PC0             | R/W        | STK5L          |

| 0F5H         | 001 01       | 551 56           | 001 00       | S5PC12          | S5PC11          | S5PC10          | S5PC9           | S5PC8             | R/W        | STK5H          |

| 0F6H         | S4PC7        | S4PC6            | S4PC5        | S4PC4           | S4PC3           | S4PC2           | S4PC1           | S4PC0             | R/W        | STK4L          |

| 0F7H         | 0 :: 07      | 3 :: 00          | 0 11 00      | S4PC12          | S4PC11          | S4PC10          | S4PC9           | S4PC8             | R/W        | STK4H          |

| 0F8H         | S3PC7        | S3PC6            | S3PC5        | S3PC4           | S3PC3           | S3PC2           | S3PC1           | S3PC0             | R/W        | STK3L          |

| 0F9H         |              |                  |              | S3PC12          | S3PC11          | S3PC10          | S3PC9           | S3PC8             | R/W        | STK3H          |

| 0FAH         | S2PC7        | S2PC6            | S2PC5        | S2PC4           | S2PC3           | S2PC2           | S2PC1           | S2PC0             | R/W        | STK2L          |

| 0FBH         |              |                  |              | S2PC12          | S2PC11          | S2PC10          | S2PC9           | S2PC8             | R/W        | STK2H          |

| 0FCH         | S1PC7        | S1PC6            | S1PC5        | S1PC4           | S1PC3           | S1PC2           | S1PC1           | S1PC0             | R/W        | STK1L          |

| 0FDH         |              |                  |              | S1PC12          | S1PC11          | S1PC10          | S1PC9           | S1PC8             | R/W        | STK1H          |

| 0FEH         | S0PC7        | S0PC6            | S0PC5        | S0PC4           | S0PC3           | S0PC2           | S0PC1           | S0PC0             | R/W        | STK0L          |

| 0FFH         |              |                  |              | S0PC12          | S0PC11          | S0PC10          | S0PC9           | S0PC8             | R/W        | STK0H          |

#### Note:

- To avoid system error, please be sure to put all the "0" and "1" as it indicates in the above table.

All of register names had been declared in SN8ASM assembler.

- 3. One-bit name had been declared in SN8ASM assembler with "F" prefix code.

- 4. "b0bset", "b0bclr", "bset", "bclr" instructions are only available to the "R/W" registers.

- 5. For detail description, please refer to the "System Register Quick Reference Table".

#### 2.1.4.4 ACCUMULATOR

The ACC is an 8-bit data register responsible for transferring or manipulating data between ALU and data memory. If the result of operating is zero (Z) or there is carry (C or DC) occurrence, then these flags will be set to PFLAG register. ACC is not in data memory (RAM), so ACC can't be access by "B0MOV" instruction during the instant addressing mode.

; Read ACC data and store in BUF data memory.

MOV

BUF, A

; Write a immediate data into ACC.

MOV

A, #0FH

; Write ACC data from BUF data memory.

MOV

A, BUF

; or

B0MOV A, BUF

The system doesn't store ACC and PFLAG value when interrupt executed. ACC and PFLAG data must be saved to other data memories. "PUSH", "POP" save and load ACC, PFLAG data into buffers.

> Example: Protect ACC and working registers.

INT\_SERVICE:

PUSH ; Save ACC and PFLAG to buffers.

• • • •

POP ; Load ACC and PFLAG from buffers.

RETI ; Exit interrupt service vector

#### 2.1.4.5 PROGRAM FLAG

The PFLAG register contains the arithmetic status of ALU operation, system reset status and LVD detecting status. NT0, NPD bits indicate system reset status including power on reset, LVD reset, reset by external pin active and watchdog reset. C, DC, Z bits indicate the result status of ALU operation.

| 086H        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| PFLAG       | NT0   | NPD   | -     | -     | -     | С     | DC    | Z     |

| Read/Write  | R/W   | R/W   | -     | -     | -     | R/W   | R/W   | R/W   |

| After reset | -     | -     | -     | -     | -     | 0     | 0     | 0     |

#### Bit [7:6] **NT0**, **NPD**: Reset status flag.

| NT0 | NPD | Reset Status                |

|-----|-----|-----------------------------|

| 0   | 0   | Watch-dog time out          |

| 0   | 1   | Reserved                    |

| 1   | 0   | Reset by LVD                |

| 1   | 1   | Reset by external Reset Pin |

#### Bit 2 C: Carry flag

- 1 = Addition with carry, subtraction without borrowing, rotation with shifting out logic "1", comparison result ≥ 0.

- 0 = Addition without carry, subtraction with borrowing signal, rotation with shifting out logic "0", comparison result < 0.

#### Bit 1 **DC:** Decimal carry flag

- 1 = Addition with carry from low nibble, subtraction without borrow from high nibble.

- 0 = Addition without carry from low nibble, subtraction with borrow from high nibble.

#### Bit 0 **Z**: Zero flag

- 1 = The result of an arithmetic/logic/branch operation is zero.

- 0 = The result of an arithmetic/logic/branch operation is not zero.

Note: Refer to instruction set table for detailed information of C, DC and Z flags.

#### 2.1.4.6 PROGRAM COUNTER

The program counter (PC) is a 13-bit binary counter separated into the high-byte 5 and the low-byte 8 bits. This counter is responsible for pointing a location in order to fetch an instruction for kernel circuit. Normally, the program counter is automatically incremented with each instruction during program execution.

Besides, it can be replaced with specific address by executing CALL or JMP instruction. When JMP or CALL instruction is executed, the destination address will be inserted to bit 0 ~ bit 12.

|             | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| PC          | -      | -      | -      | PC12   | PC11   | PC10   | PC9   | PC8   | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

| After reset | -      | ı      | -      | 0      | 0      | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|             | PCH    |        |        |        |        |        |       |       |       |       |       | P(    | CL    |       |       |       |

#### **ONE ADDRESS SKIPPING**

There are nine instructions (CMPRS, INCS, INCMS, DECS, DECMS, BTS0, BTS1, B0BTS0, B0BTS1) with one address skipping function. If the result of these instructions is true, the PC will add 2 steps to skip next instruction.

If the condition of bit test instruction is true, the PC will add 2 steps to skip next instruction.

B0BTS1 FC ; To skip, if Carry flag = 1 ; Else jump to C0STEP. **JMP COSTEP**

. . .

COSTEP: NOP

> **B0MOV** A, BUF0 ; Move BUF0 value to ACC. ; To skip, if Zero flag = 0. **B0BTS0** FΖ C1STEP ; Else jump to C1STEP.

**JMP**

C1STEP: NOP

If the ACC is equal to the immediate data or memory, the PC will add 2 steps to skip next instruction.

**CMPRS** A, #12H ; To skip, if ACC = 12H. **JMP COSTEP** ; Else jump to COSTEP.

COSTEP: NOP

If the destination increased by 1, which results overflow of 0xFF to 0x00, the PC will add 2 steps to skip next instruction.

**INCS** instruction:

INCS BUF0

JMP COSTEP ; Jump to COSTEP if ACC is not zero.

• • •

COSTEP: NOP

**INCMS** instruction:

INCMS BUF0

JMP COSTEP ; Jump to COSTEP if BUF0 is not zero.

. . .

COSTEP: NOP

If the destination decreased by 1, which results underflow of 0x00 to 0xFF, the PC will add 2 steps to skip next instruction.

**DECS** instruction:

**DECS** BUF0

JMP COSTEP ; Jump to COSTEP if ACC is not zero.

• • •

COSTEP: NOP

**DECMS** instruction:

**DECMS** BUF0

JMP COSTEP ; Jump to COSTEP if BUF0 is not zero.

• • •

COSTEP: NOP

#### MULTI-ADDRESS JUMPING

Users can jump around the multi-address by either JMP instruction or ADD M, A instruction (M = PCL) to activate multi-address jumping function. Program Counter supports "ADD M,A", "ADC M,A" and "B0ADD M,A" instructions for carry to PCH when PCL overflow automatically. For jump table or others applications, users can calculate PC value by the three instructions and don't care PCL overflow problem.

Note: PCH only support PC up counting result and doesn't support PC down counting. When PCL is carry after PCL+ACC, PCH adds one automatically. If PCL borrow after PCL-ACC, PCH keeps value and not change.

Example: If PC = 0323H (PCH = 03H, PCL = 23H)

; PC = 0323H

MOV A, #28H

B0MOV PCL, A ; Jump to address 0328H

...

; PC = 0328H

MOV A, #00H

B0MOV PCL, A ; Jump to address 0300H

...

> Example: If PC = 0323H (PCH = 03H, PCL = 23H)

; PC = 0323H

BOADD PCL, A ; PCL = PCL + ACC, the PCH cannot be changed.

• •

. . .

#### **2.1.4.7 Y, Z REGISTERS**

The Y and Z registers are the 8-bit buffers. There are three major functions of these registers.

- can be used as general working registers

- can be used as RAM data pointers with @YZ register

- can be used as ROM data pointer with the MOVC instruction for look-up table

| 083H        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Z           | ZBIT7 | ZBIT6 | ZBIT5 | ZBIT4 | ZBIT3 | ZBIT2 | ZBIT1 | ZBIT0 |

| Read/Write  | R/W   |

| After reset | -     | -     | -     | -     | -     | -     | -     | -     |

| 084H        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Υ           | YBIT7 | YBIT6 | YBIT5 | YBIT4 | YBIT3 | YBIT2 | YBIT1 | YBIT0 |

| Read/Write  | R/W   |

| After reset | -     | -     | -     | -     | -     | -     | -     | -     |

Example: Uses Y, Z register as the data pointer to access data in the RAM address 025H of bank0.

B0MOV Y, #00H ; To set RAM bank 0 for Y register B0MOV Z, #25H ; To set location 25H for Z register

B0MOV A, @YZ ; To read a data into ACC

Example: Uses the Y, Z register as data pointer to clear the RAM data.

B0MOV Y, #0 ; Y = 0, bank 0

B0MOV Z, #07FH ; Z = 7FH, the last address of the data memory area

CLR\_YZ\_BUF:

CLR @YZ ; Clear @YZ to be zero

DECMS Z ; Z - 1, if Z = 0, finish the routine

JMP CLR YZ BUF ; Not zero

CLR @YZ

END\_CLR: ; End of clear general purpose data memory area of bank 0

...

#### **2.1.4.8 R REGISTERS**

R register is an 8-bit buffer. There are two major functions of the register.

- Can be used as working register

- For store high-byte data of look-up table

(MOVC instruction executed, the high-byte data of specified ROM address will be stored in R register and the low-byte data will be stored in ACC).

| 082H        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| R           | RBIT7 | RBIT6 | RBIT5 | RBIT4 | RBIT3 | RBIT2 | RBIT1 | RBIT0 |

| Read/Write  | R/W   |

| After reset | -     | -     | -     | -     | -     | -     | -     | -     |

Note: Please refer to the "LOOK-UP TABLE DESCRIPTION" about R register look-up table application.

## 2.2 ADDRESSING MODE

#### 2.2.1 IMMEDIATE ADDRESSING MODE

The immediate addressing mode uses an immediate data to set up the location in ACC or specific RAM.

> Example: Move the immediate data 12H to ACC.

MOV A, #12H ; To set an immediate data 12H into ACC.

> Example: Move the immediate data 12H to R register.

B0MOV R, #12H ; To set an immediate data 12H into R register.

Note: In immediate addressing mode application, the specific RAM must be 0x80~0x87 working register.

#### 2.2.2 DIRECTLY ADDRESSING MODE

The directly addressing mode moves the content of RAM location in or out of ACC.

Example: Move 0x12 RAM location data into ACC.

B0MOV A, 12H ; To get a content of RAM location 0x12 of bank 0 and save in

ACC.

Example: Move ACC data into 0x12 RAM location.

B0MOV 12H, A ; To get a content of ACC and save in RAM location 12H of

bank 0.

#### 2.2.3 INDIRECTLY ADDRESSING MODE

The indirectly addressing mode is to access the memory by the data pointer registers (Y/Z).

> Example: Indirectly addressing mode with @YZ register.

B0MOV Y, #0 ; To clear Y register to access RAM bank 0. B0MOV Z, #12H ; To set an immediate data 12H into Z register.

B0MOV A, @YZ ; Use data pointer @YZ reads a data from RAM location

; 012H into ACC.

## 2.3 STACK OPERATION

#### 2.3.1 OVERVIEW

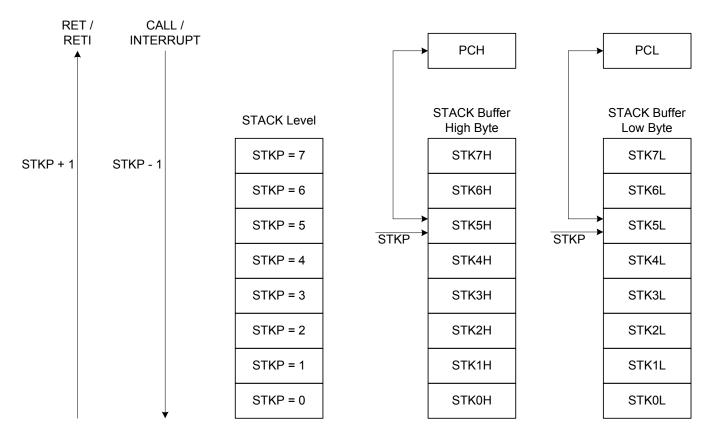

The stack buffer has 8-level. These buffers are designed to push and pop up program counter's (PC) data when interrupt service routine and "CALL" instruction are executed. The STKP register is a pointer designed to point active level in order to push or pop up data from stack buffer. The STKnH and STKnL are the stack buffers to store program counter (PC) data.

#### 2.3.2 STACK REGISTERS

The stack pointer (STKP) is a 3-bit register to store the address used to access the stack buffer, 13-bit data memory (STKnH and STKnL) set aside for temporary storage of stack addresses.

The two stack operations are writing to the top of the stack (push) and reading from the top of stack (pop). Push operation decrements the STKP and the pop operation increments each time. That makes the STKP always point to the top address of stack buffer and write the last program counter value (PC) into the stack buffer.

The program counter (PC) value is stored in the stack buffer before a CALL instruction executed or during interrupt service routine. Stack operation is a LIFO type (Last in and first out). The stack pointer (STKP) and stack buffer (STKnH and STKnL) are located in the system register area bank 0.

| 0DFH        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  |

|-------------|-------|-------|-------|-------|-------|--------|--------|--------|

| STKP        | GIE   | -     | -     | -     | -     | STKPB2 | STKPB1 | STKPB0 |

| Read/Write  | R/W   | -     | -     | -     | -     | R/W    | R/W    | R/W    |

| After reset | 0     | -     | -     | -     | -     | 1      | 1      | 1      |

Bit[2:0] **STKPBn:** Stack pointer (n =  $0 \sim 2$ )

Bit 7 GIE: Global interrupt control bit.

0 = Disable.

1 = Enable. Please refer to the interrupt chapter.

Example: Stack pointer (STKP) reset, we strongly recommended to clear the stack pointers in the beginning of the program.

MOV A, #00000111B B0MOV STKP, A

| 0F0H~0FFH   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|--------|--------|--------|-------|-------|

| STKnH       | -     | -     | -     | SnPC12 | SnPC11 | SnPC10 | SnPC9 | SnPC8 |

| Read/Write  | -     | -     | -     | R/W    | R/W    | R/W    | R/W   | R/W   |

| After reset | ı     | -     | ı     | 0      | 0      | 0      | 0     | 0     |

| 0F0H~0FFH   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| STKnL       | SnPC7 | SnPC6 | SnPC5 | SnPC4 | SnPC3 | SnPC2 | SnPC1 | SnPC0 |

| Read/Write  | R/W   |

| After reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

STKn = STKnH, STKnL  $(n = 7 \sim 0)$

#### 2.3.3 STACK OPERATION EXAMPLE

The two kinds of Stack-Save operations refer to the stack pointer (STKP) and write the content of program counter (PC) to the stack buffer are CALL instruction and interrupt service. Under each condition, the STKP decreases and points to the next available stack location. The stack buffer stores the program counter about the op-code address. The Stack-Save operation is as the following table.

| Stack Level | S      | TKP Registe | er     | Stack     | Buffer   | Description       |  |

|-------------|--------|-------------|--------|-----------|----------|-------------------|--|

| Stack Level | STKPB2 | STKPB1      | STKPB0 | High Byte | Low Byte | Description       |  |

| 0           | 1      | 1           | 1      | Free      | Free     | -                 |  |

| 1           | 1      | 1           | 0      | STK0H     | STK0L    | -                 |  |

| 2           | 1      | 0           | 1      | STK1H     | STK1L    | -                 |  |

| 3           | 1      | 0           | 0      | STK2H     | STK2L    | =                 |  |

| 4           | 0      | 1           | 1      | STK3H     | STK3L    | -                 |  |

| 5           | 0      | 1           | 0      | STK4H     | STK4L    | -                 |  |

| 6           | 0      | 0           | 1      | STK5H     | STK5L    | -                 |  |

| 7           | 0      | 0           | 0      | STK6H     | STK6L    | -                 |  |

| 8           | 1      | 1           | 1      | STK7H     | STK7L    | -                 |  |

| > 8         | 1      | 1           | 0      | -         | -        | Stack Over, error |  |

There are Stack-Restore operations correspond to each push operation to restore the program counter (PC). The RETI instruction uses for interrupt service routine. The RET instruction is for CALL instruction. When a pop operation occurs, the STKP is incremented and points to the next free stack location. The stack buffer restores the last program counter (PC) to the program counter registers. The Stack-Restore operation is as the following table.

| Stack Level | S      | TKP Registe | er     | Stack     | Buffer   | Description |  |

|-------------|--------|-------------|--------|-----------|----------|-------------|--|

|             | STKPB2 | STKPB1      | STKPB0 | High Byte | Low Byte | Description |  |

| 8           | 1      | 1           | 1      | STK7H     | STK7L    | =           |  |

| 7           | 0      | 0           | 0      | STK6H     | STK6L    | =           |  |

| 6           | 0      | 0           | 1      | STK5H     | STK5L    | -           |  |

| 5           | 0      | 1           | 0      | STK4H     | STK4L    | =           |  |

| 4           | 0      | 1           | 1      | STK3H     | STK3L    | -           |  |

| 3           | 1      | 0           | 0      | STK2H     | STK2L    | -           |  |

| 2           | 1      | 0           | 1      | STK1H     | STK1L    | -           |  |

| 1           | 1      | 1           | 0      | STK0H     | STK0L    | -           |  |

| 0           | 1      | 1           | 1      | Free      | Free     | -           |  |

# 3 RESET

### 3.1 OVERVIEW

The system would be reset in three conditions as following.

- Power on reset

- Watchdog reset

- Brown out reset

- External reset (only supports external reset pin enable situation)

When any reset condition occurs, all system registers keep initial status, program stops and program counter is cleared. After reset status released, the system boots up and program starts to execute from ORG 0. The NT0, NPD flags indicate system reset status. The system can depend on NT0, NPD status and go to different paths by program.

| 086H        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| PFLAG       | NT0   | NPD   | -     | -     | -     | С     | DC    | Z     |

| Read/Write  | R/W   | R/W   | -     | -     | -     | R/W   | R/W   | R/W   |

| After reset | -     | -     | -     | -     | -     | 0     | 0     | 0     |

### Bit [7:6] NT0, NPD: Reset status flag.

| NT0 | NPD | Condition                     | Description                                      |

|-----|-----|-------------------------------|--------------------------------------------------|

| 0   | 0   | Watchdog reset                | Watchdog timer overflow.                         |

| 0   | 1   | Reserved                      | -                                                |

| 1   | 0   | Power on reset and LVD reset. | Power voltage is lower than LVD detecting level. |

| 1   | 1   | External reset                | External reset pin detect low level status.      |

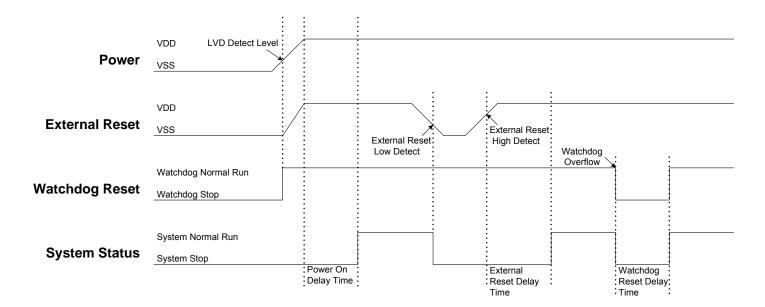

Finishing any reset sequence needs some time. The system provides complete procedures to make the power on reset successful. For different oscillator types, the reset time is different. That causes the VDD rise rate and start-up time of different oscillator is not fixed. RC type oscillator's start-up time is very short, but the crystal type is longer. Under client terminal application, users have to take care the power on reset time for the master terminal requirement. The reset timing diagram is as following.

### 3.2 POWER ON RESET

The power on reset depend no LVD operation for most power-up situations. The power supplying to system is a rising curve and needs some time to achieve the normal voltage. Power on reset sequence is as following.

- **Power-up:** System detects the power voltage up and waits for power stable.

- External reset (only external reset pin enable): System checks external reset pin status. If external reset pin is not high level, the system keeps reset status and waits external reset pin released.

- System initialization: All system registers is set as initial conditions and system is ready.

- Oscillator warm up: Oscillator operation is successfully and supply to system clock.

- Program executing: Power on sequence is finished and program executes from ORG 0.

### 3.3 WATCHDOG RESET

Watchdog reset is a system protection. In normal condition, system works well and clears watchdog timer by program. Under error condition, system is in unknown situation and watchdog can't be clear by program before watchdog timer overflow. Watchdog timer overflow occurs and the system is reset. After watchdog reset, the system restarts and returns normal mode. Watchdog reset sequence is as following.

- Watchdog timer status: System checks watchdog timer overflow status. If watchdog timer overflow occurs, the system is reset.

- System initialization: All system registers is set as initial conditions and system is ready.

- Oscillator warm up: Oscillator operation is successfully and supply to system clock.

- Program executing: Power on sequence is finished and program executes from ORG 0.

Watchdog timer application note is as following.

- Before clearing watchdog timer, check I/O status and check RAM contents can improve system error.

- Don't clear watchdog timer in interrupt vector and interrupt service routine. That can improve main routine fail.

- Clearing watchdog timer program is only at one part of the program. This way is the best structure to enhance the watchdog timer function.

- Note: Please refer to the "WATCHDOG TIMER" about watchdog timer detail information.

### 3.4 BROWN OUT RESET

### 3.4.1 BROWN OUT DESCRIPTION

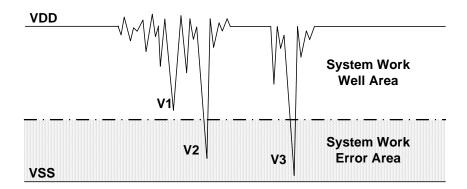

The brown out reset is a power dropping condition. The power drops from normal voltage to low voltage by external factors (e.g. EFT interference or external loading changed). The brown out reset would make the system not work well or executing program error.

**Brown Out Reset Diagram**

The power dropping might through the voltage range that's the system dead-band. The dead-band means the power range can't offer the system minimum operation power requirement. The above diagram is a typical brown out reset diagram. There is a serious noise under the VDD, and VDD voltage drops very deep. There is a dotted line to separate the system working area. The above area is the system work well area. The below area is the system work error area called dead-band. V1 doesn't touch the below area and not effect the system operation. But the V2 and V3 is under the below area and may induce the system error occurrence. Let system under dead-band includes some conditions.

#### DC application:

The power source of DC application is usually using battery. When low battery condition and MCU drive any loading, the power drops and keeps in dead-band. Under the situation, the power won't drop deeper and not touch the system reset voltage. That makes the system under dead-band.

### AC application:

In AC power application, the DC power is regulated from AC power source. This kind of power usually couples with AC noise that makes the DC power dirty. Or the external loading is very heavy, e.g. driving motor. The loading operating induces noise and overlaps with the DC power. VDD drops by the noise, and the system works under unstable power situation.

The power on duration and power down duration are longer in AC application. The system power on sequence protects the power on successful, but the power down situation is like DC low battery condition. When turn off the AC power, the VDD drops slowly and through the dead-band for a while.

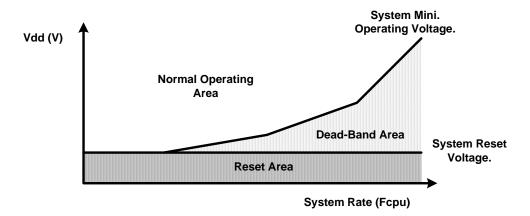

### 3.4.2 THE SYSTEM OPERATING VOLTAGE DECSRIPTION

To improve the brown out reset needs to know the system minimum operating voltage which is depend on the system executing rate and power level. Different system executing rates have different system minimum operating voltage. The electrical characteristic section shows the system voltage to executing rate relationship.

Normally the system operation voltage area is higher than the system reset voltage to VDD, and the reset voltage is decided by LVD detect level. The system minimum operating voltage rises when the system executing rate upper even higher than system reset voltage. The dead-band definition is the system minimum operating voltage above the system reset voltage.

### 3.4.3 BROWN OUT RESET IMPROVEMENT

How to improve the brown reset condition? There are some methods to improve brown out reset as following.

- LVD reset

- Watchdog reset

- Reduce the system executing rate

- External reset circuit. (Zener diode reset circuit, Voltage bias reset circuit, External reset IC)

#### \* Note:

- 1. The "Zener diode reset circuit", "Voltage bias reset circuit" and "External reset IC" can completely improve the brown out reset, DC low battery and AC slow power down conditions.

- 2. For AC power application and enhance EFT performance, the system clock is 4MHz/4 (1 mips) and use external reset (" Zener diode reset circuit", "Voltage bias reset circuit", "External reset IC"). The structure can improve noise effective and get good EFT characteristic.

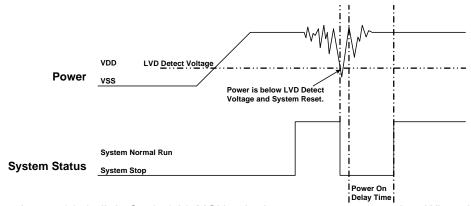

#### LVD reset:

The LVD (low voltage detector) is built-in Sonix 8-bit MCU to be brown out reset protection. When the VDD drops and is below LVD detect voltage, the LVD would be triggered, and the system is reset. The LVD detect level is different by each MCU. The LVD voltage level is a point of voltage and not easy to cover all dead-band range. Using LVD to improve brown out reset is depend on application requirement and environment. If the power variation is very deep, violent and trigger the LVD, the LVD can be the protection. If the power variation can touch the LVD detect level and make system work error, the LVD can't be the protection and need to other reset methods. More detail LVD information is in the electrical characteristic section.

### Watchdog reset:

The watchdog timer is a protection to make sure the system executes well. Normally the watchdog timer would be clear at one point of program. Don't clear the watchdog timer in several addresses. The system executes normally and the watchdog won't reset system. When the system is under dead-band and the execution error, the watchdog timer can't be clear by program. The watchdog is continuously counting until overflow occurrence. The overflow signal of watchdog timer triggers the system to reset, and the system return to normal mode after reset sequence. This method also can improve brown out reset condition and make sure the system to return normal mode. If the system reset by watchdog and the power is still in dead-band, the system reset sequence won't be successful and the system stays in reset status until the power return to normal range.

### Reduce the system executing rate:

If the system rate is fast and the dead-band exists, to reduce the system executing rate can improve the dead-band. The lower system rate is with lower minimum operating voltage. Select the power voltage that's no dead-band issue and find out the mapping system rate. Adjust the system rate to the value and the system exits the dead-band issue. This way needs to modify whole program timing to fit the application requirement.

### **External reset circuit:**

The external reset methods also can improve brown out reset and is the complete solution. There are three external reset circuits to improve brown out reset including "Zener diode reset circuit", "Voltage bias reset circuit" and "External reset IC". These three reset structures use external reset signal and control to make sure the MCU be reset under power dropping and under dead-band. The external reset information is described in the next section.

### 3.5 EXTERNAL RESET

External reset function is controlled by "Reset\_Pin" code option. Set the code option as "Reset" option to enable external reset function. External reset pin is Schmitt Trigger structure and low level active. The system is running when reset pin is high level voltage input. The reset pin receives the low voltage and the system is reset. The external reset operation actives in power on and normal running mode. During system power-up, the external reset pin must be high level input, or the system keeps in reset status. External reset sequence is as following.

- External reset (only external reset pin enable): System checks external reset pin status. If external reset pin is not high level, the system keeps reset status and waits external reset pin released.

- System initialization: All system registers is set as initial conditions and system is ready.

- Oscillator warm up: Oscillator operation is successfully and supply to system clock.

- Program executing: Power on sequence is finished and program executes from ORG 0.

The external reset can reset the system during power on duration, and good external reset circuit can protect the system to avoid working at unusual power condition, e.g. brown out reset in AC power application...

### 3.6 EXTERNAL RESET CIRCUIT

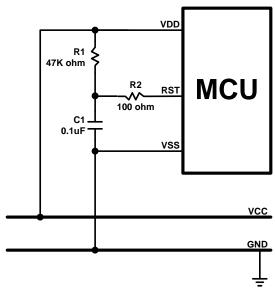

### 3.6.1 Simply RC Reset Circuit

This is the basic reset circuit, and only includes R1 and C1. The RC circuit operation makes a slow rising signal into reset pin as power up. The reset signal is slower than VDD power up timing, and system occurs a power on signal from the timing difference.

Note: The reset circuit is no any protection against unusual power or brown out reset.

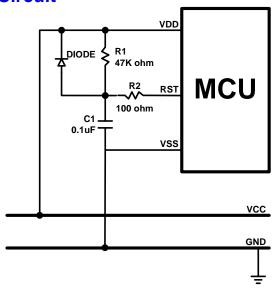

### 3.6.2 Diode & RC Reset Circuit

This is the better reset circuit. The R1 and C1 circuit operation is like the simply reset circuit to make a power on signal. The reset circuit has a simply protection against unusual power. The diode offers a power positive path to conduct higher power to VDD. It is can make reset pin voltage level to synchronize with VDD voltage. The structure can improve slight brown out reset condition.